在上一部分介紹了集成電路(IC)的基本分類和設(shè)計流程概覽后,我們進(jìn)一步聚焦于超大規(guī)模集成電路(VLSI)設(shè)計的核心概念與環(huán)節(jié)。VLSI設(shè)計是微電子領(lǐng)域的皇冠,它涉及將數(shù)百萬乃至數(shù)十億個晶體管集成到單一芯片上,以實現(xiàn)復(fù)雜的功能。

1. 設(shè)計層次與抽象

VLSI設(shè)計通常在多個抽象層次上進(jìn)行,這是一種“分而治之”的策略,以管理極端復(fù)雜性。

- 系統(tǒng)級:定義芯片的總體功能、性能指標(biāo)和模塊劃分。

- 行為級:使用硬件描述語言(如Verilog、VHDL)描述各模塊的邏輯功能,不涉及具體電路結(jié)構(gòu)。

- 寄存器傳輸級(RTL):描述數(shù)據(jù)在寄存器之間的流動和轉(zhuǎn)換,是邏輯綜合的起點,也是設(shè)計驗證的核心層級。

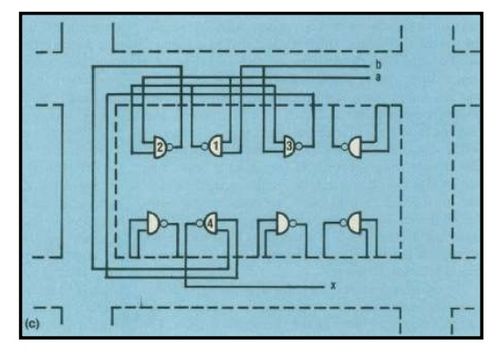

- 邏輯門級:由基本邏輯門(如與門、或門、非門)和觸發(fā)器構(gòu)成的網(wǎng)表。

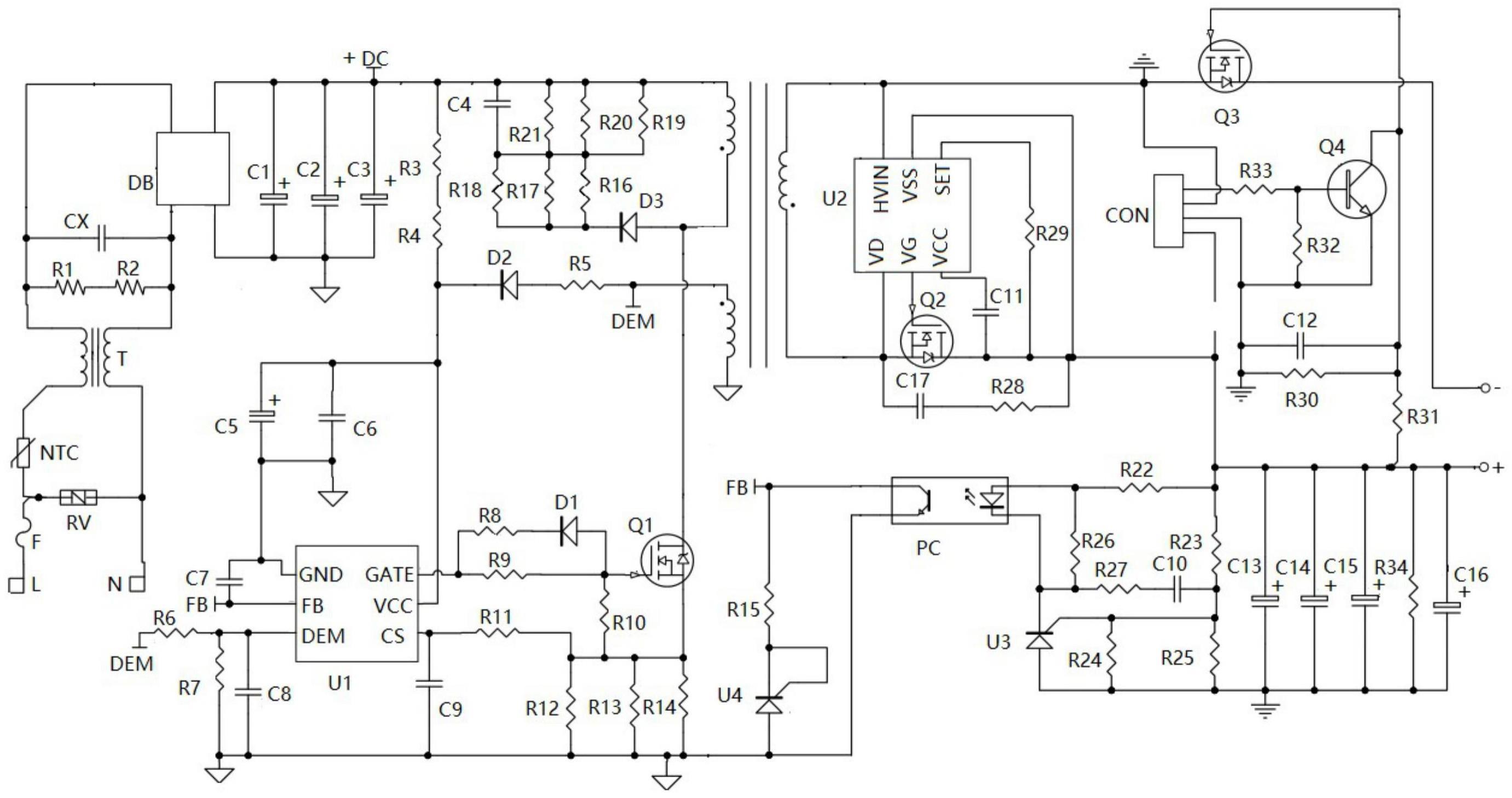

- 電路級:關(guān)注晶體管的具體連接方式,構(gòu)成邏輯門的物理實現(xiàn),分析時序、功耗等電氣特性。

- 版圖級:將電路轉(zhuǎn)換為制造所需的幾何圖形(多邊形),定義晶體管、連線的物理形狀、尺寸和位置。

設(shè)計過程通常是一個自上而下(Top-Down)的設(shè)計與自下而上(Bottom-Up)的驗證相結(jié)合的過程。

2. 設(shè)計方法學(xué)與流程核心

現(xiàn)代VLSI設(shè)計高度依賴于電子設(shè)計自動化(EDA)工具和嚴(yán)格的方法學(xué)。

- 邏輯綜合:將RTL代碼自動轉(zhuǎn)換為優(yōu)化后的門級網(wǎng)表,是連接高層次設(shè)計與物理實現(xiàn)的關(guān)鍵橋梁。綜合工具會根據(jù)設(shè)計約束(時序、面積、功耗)和工藝庫進(jìn)行優(yōu)化。

- 驗證:貫穿整個設(shè)計流程,確保設(shè)計正確性。主要包括:

- 功能驗證:通過仿真、形式驗證等方法,檢查設(shè)計行為是否符合規(guī)格要求。

- 時序驗證:在布局布線后,提取寄生參數(shù),進(jìn)行靜態(tài)時序分析(STA),確保在所有工藝角和環(huán)境下滿足時序要求。

- 物理驗證:檢查版圖是否符合制造規(guī)則(DRC)、電路與版圖是否一致(LVS)等。

- 可測性設(shè)計(DFT):為了提高芯片生產(chǎn)后的測試覆蓋率,在設(shè)計階段就插入掃描鏈、內(nèi)建自測試(BIST)等結(jié)構(gòu),使得芯片內(nèi)部節(jié)點能夠被控制和觀測。

- 低功耗設(shè)計:隨著工藝進(jìn)步,功耗密度成為巨大挑戰(zhàn)。技術(shù)包括時鐘門控、電源門控、多電壓域、動態(tài)電壓頻率調(diào)節(jié)(DVFS)等。

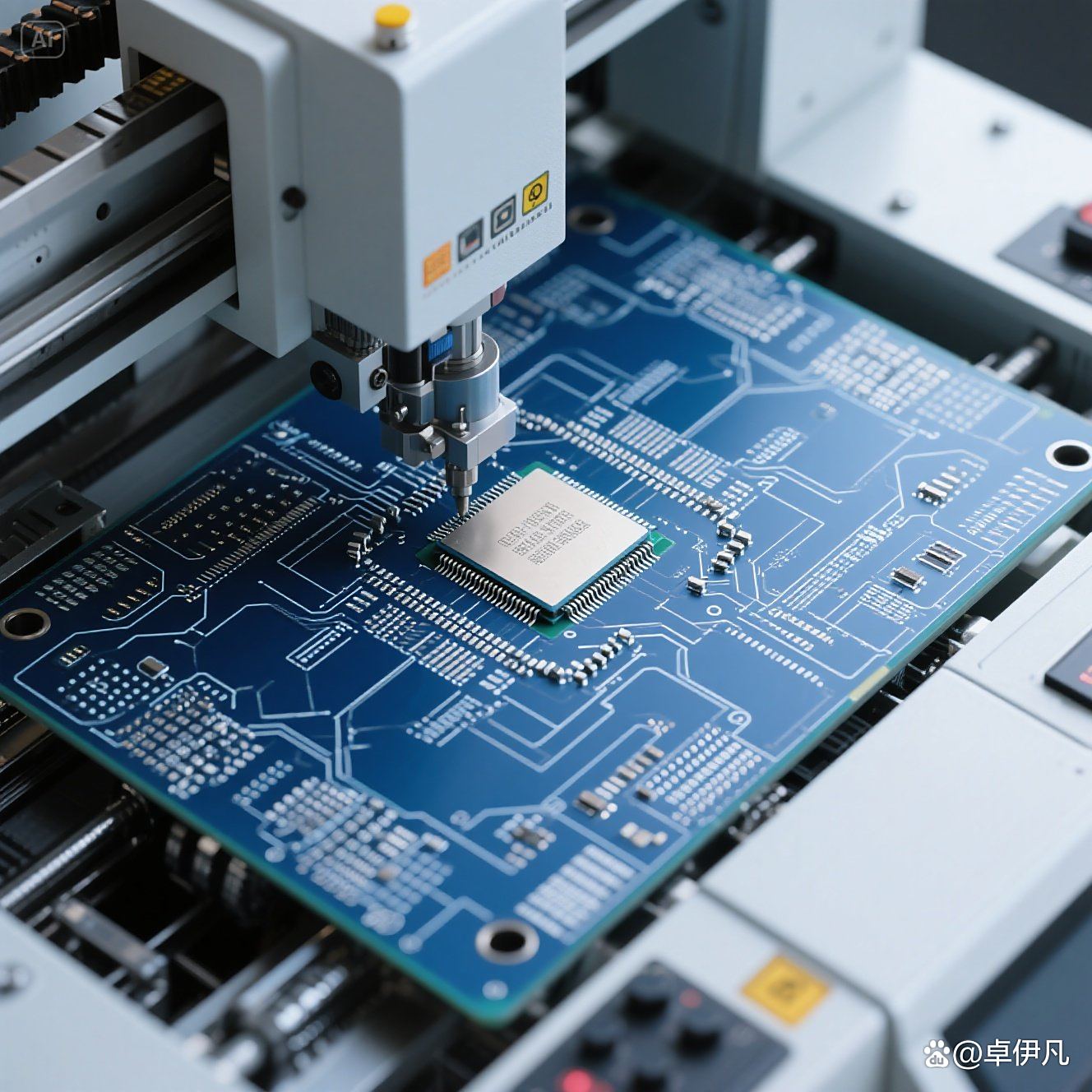

3. 物理設(shè)計:從網(wǎng)表到芯片

物理設(shè)計是將邏輯網(wǎng)表轉(zhuǎn)化為可制造的幾何版圖的過程,主要包括以下步驟:

- 布圖規(guī)劃:確定芯片核心區(qū)域、模塊的大致位置和輸入輸出(I/O)單元排列,規(guī)劃電源網(wǎng)絡(luò)。

- 布局:確定標(biāo)準(zhǔn)單元和宏模塊在芯片上的精確位置,目標(biāo)是減少連線長度和時序延遲。

- 時鐘樹綜合(CTS):構(gòu)建一個低偏斜、低延遲的全局時鐘分布網(wǎng)絡(luò),確保時鐘信號同步到達(dá)所有時序單元。

- 布線:根據(jù)布局結(jié)果,完成單元之間所有邏輯信號的物理連接。分為全局布線和詳細(xì)布線兩步。

- 簽核:在交付制造前的最終驗證階段,進(jìn)行全面的時序、功耗、信號完整性和物理驗證。

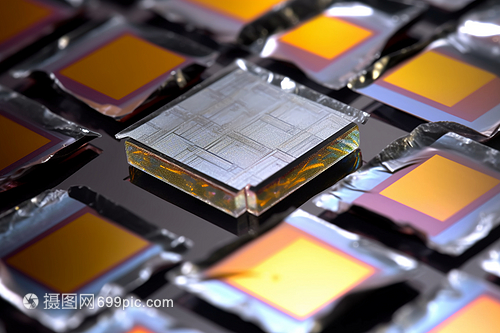

4. 工藝與設(shè)計協(xié)同優(yōu)化

VLSI設(shè)計與半導(dǎo)體制造工藝緊密耦合。先進(jìn)的工藝節(jié)點(如7nm、5nm)帶來了性能提升和面積縮小,但也引入了短溝道效應(yīng)、寄生效應(yīng)加劇、制造變異增大等挑戰(zhàn)。這要求設(shè)計時必須考慮工藝角、器件模型和設(shè)計規(guī)則,甚至采用新的器件結(jié)構(gòu)(如FinFET)和設(shè)計技術(shù)協(xié)同優(yōu)化(DTCO)方法。

###

超大規(guī)模集成電路設(shè)計是一個融合了計算機(jī)科學(xué)、電子工程、物理學(xué)和數(shù)學(xué)的深度交叉學(xué)科。掌握其基本概念是理解現(xiàn)代芯片如何從抽象想法變?yōu)槭种袑嶓w設(shè)備的基礎(chǔ)。隨著人工智能、異構(gòu)計算等新需求的涌現(xiàn),VLSI設(shè)計方法學(xué)仍在不斷演進(jìn),持續(xù)推動著信息技術(shù)的邊界。