在數(shù)字集成電路設(shè)計(jì)中,抖動(dòng)(Jitter)是一個(gè)至關(guān)重要且普遍存在的現(xiàn)象。它本質(zhì)上是數(shù)字信號(hào)邊沿相對(duì)于理想時(shí)序位置的微小、快速、非確定性偏移。這種看似微小的時(shí)序偏差,在高速、高精度集成電路中卻可能引發(fā)災(zāi)難性的后果,深刻影響系統(tǒng)的性能、可靠性與穩(wěn)定性。

抖動(dòng)的核心成因

抖動(dòng)的產(chǎn)生源于多種因素的綜合作用,主要可歸納為以下幾類(lèi):

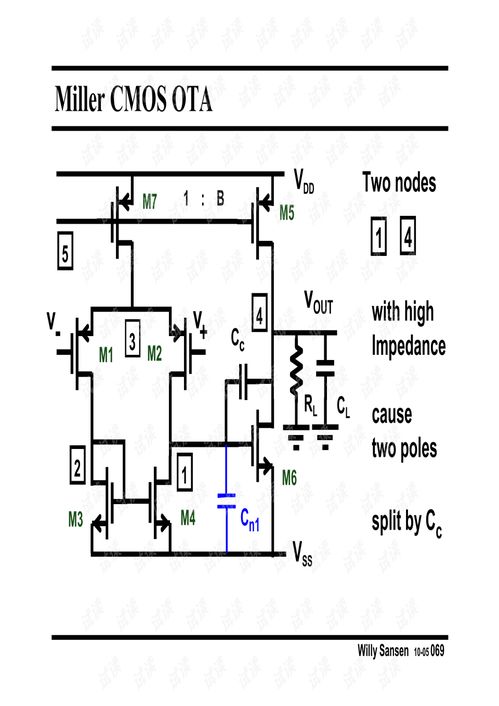

- 內(nèi)部噪聲:這是抖動(dòng)最根本的來(lái)源之一。電路中晶體管的熱噪聲(約翰遜-奈奎斯特噪聲)、閃爍噪聲(1/f噪聲)以及電源/襯底噪聲等,都會(huì)直接調(diào)制信號(hào)的渡越時(shí)間,導(dǎo)致邊沿到達(dá)時(shí)刻的隨機(jī)波動(dòng)。

- 電源完整性與信號(hào)完整性(PI/SI)問(wèn)題:電源網(wǎng)絡(luò)的波動(dòng)(如地彈、電源噪聲)會(huì)通過(guò)器件閾值電壓等參數(shù)影響開(kāi)關(guān)速度。傳輸線上的反射、串?dāng)_等信號(hào)完整性問(wèn)題會(huì)扭曲信號(hào)波形,改變其過(guò)零點(diǎn),從而引入確定性抖動(dòng)。

- 時(shí)鐘分配網(wǎng)絡(luò)的不完美:時(shí)鐘路徑上的緩沖器延時(shí)偏差、互連線延時(shí)差異以及時(shí)鐘樹(shù)上的噪聲注入,都會(huì)導(dǎo)致時(shí)鐘邊沿到達(dá)各觸發(fā)器的時(shí)間不一致,即時(shí)鐘抖動(dòng)。這是系統(tǒng)級(jí)時(shí)序違例的主要誘因之一。

- 工藝、電壓、溫度(PVT)變化:制造工藝的微觀差異、工作電壓的波動(dòng)以及環(huán)境溫度的變化,會(huì)導(dǎo)致器件參數(shù)(如遷移率、閾值電壓)漂移,從而引起信號(hào)傳播延時(shí)的系統(tǒng)性或隨機(jī)性變化。

抖動(dòng)對(duì)數(shù)字電路的影響

抖動(dòng)的影響是全方位的,其嚴(yán)重性隨電路速度的提升而指數(shù)級(jí)增加:

- 時(shí)序違例與功能錯(cuò)誤:過(guò)大的抖動(dòng)會(huì)侵蝕系統(tǒng)的時(shí)序裕量。對(duì)于建立時(shí)間/保持時(shí)間檢查,時(shí)鐘或數(shù)據(jù)的抖動(dòng)可能直接導(dǎo)致觸發(fā)器采樣錯(cuò)誤,引發(fā)功能故障。在高速串行接口(如SerDes)中,抖動(dòng)會(huì)直接縮小數(shù)據(jù)有效采樣窗口,增加誤碼率。

- 性能降級(jí):為了容忍一定程度的抖動(dòng),設(shè)計(jì)者往往被迫降低系統(tǒng)最高工作頻率或增加時(shí)鐘周期,從而犧牲了性能。

- 功耗增加:在時(shí)鐘路徑中,為了抑制抖動(dòng)(如使用鎖相環(huán)PLL進(jìn)行濾波和抖動(dòng)衰減),需要增加電路復(fù)雜度,這會(huì)帶來(lái)額外的功耗開(kāi)銷(xiāo)。

- 測(cè)試與驗(yàn)證挑戰(zhàn):抖動(dòng)具有隨機(jī)性和統(tǒng)計(jì)特性,使得電路在最壞情況下的時(shí)序分析變得異常復(fù)雜,增加了設(shè)計(jì)驗(yàn)證和測(cè)試的成本與難度。

集成電路設(shè)計(jì)中的抖動(dòng)應(yīng)對(duì)策略

應(yīng)對(duì)抖動(dòng)是一個(gè)貫穿設(shè)計(jì)始終的系統(tǒng)性工程:

- 設(shè)計(jì)階段的建模與預(yù)算:在架構(gòu)和電路設(shè)計(jì)初期,就需要對(duì)整系統(tǒng)的抖動(dòng)進(jìn)行建模和預(yù)算分配。為時(shí)鐘發(fā)生器、時(shí)鐘分配網(wǎng)絡(luò)、數(shù)據(jù)路徑等不同模塊設(shè)定嚴(yán)格的抖動(dòng)指標(biāo)(如周期抖動(dòng)、周期周期抖動(dòng)、時(shí)間間隔誤差)。

- 電路級(jí)抑制技術(shù):

- 采用低噪聲的電源調(diào)節(jié)器(如LDO)和精心設(shè)計(jì)的電源分配網(wǎng)絡(luò)(PDN),使用大量的去耦電容來(lái)濾除高頻電源噪聲。

- 設(shè)計(jì)對(duì)電源噪聲不敏感的電路結(jié)構(gòu),如差分邏輯、電流模邏輯(CML)或在關(guān)鍵路徑上使用高電源抑制比(PSRR)的緩沖器。

- 使用高性能的時(shí)鐘生成與調(diào)理電路,如帶抖動(dòng)衰減功能的低噪聲PLL、延遲鎖相環(huán)(DLL)。

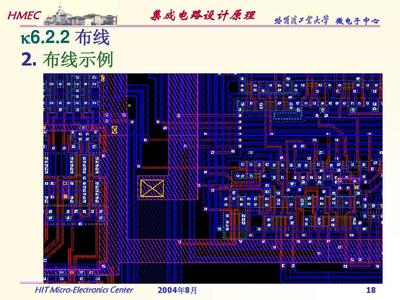

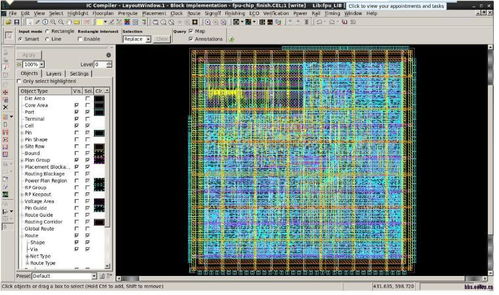

- 布局布線(物理實(shí)現(xiàn))優(yōu)化:

- 對(duì)時(shí)鐘網(wǎng)絡(luò)進(jìn)行對(duì)稱(chēng)化、屏蔽和精心的樹(shù)形結(jié)構(gòu)設(shè)計(jì),以最小化偏斜和噪聲耦合。

- 確保電源和地網(wǎng)絡(luò)的低阻抗特性,將敏感模擬/時(shí)鐘模塊與數(shù)字開(kāi)關(guān)噪聲源進(jìn)行物理隔離。

- 控制關(guān)鍵信號(hào)線的長(zhǎng)度、阻抗匹配,減少反射和串?dāng)_。

- 系統(tǒng)級(jí)與架構(gòu)級(jí)技術(shù):

- 采用彈性電路或容錯(cuò)時(shí)序設(shè)計(jì),如使用可調(diào)延時(shí)線、時(shí)間借位技術(shù)或異步電路設(shè)計(jì)范式,來(lái)吸收或容忍一定范圍內(nèi)的抖動(dòng)。

- 在高速串行鏈路中,使用均衡、時(shí)鐘數(shù)據(jù)恢復(fù)(CDR)電路和先進(jìn)的編碼方案來(lái)對(duì)抗抖動(dòng)帶來(lái)的影響。

抖動(dòng)是現(xiàn)代數(shù)字集成電路設(shè)計(jì)中一個(gè)無(wú)法回避的核心挑戰(zhàn)。深入理解其物理根源,在設(shè)計(jì)全流程中對(duì)其進(jìn)行精準(zhǔn)的建模、嚴(yán)格的控制與有效的管理,是確保芯片在高速運(yùn)行下依然穩(wěn)定可靠的關(guān)鍵所在。隨著工藝節(jié)點(diǎn)不斷演進(jìn)和系統(tǒng)頻率持續(xù)攀升,對(duì)抖動(dòng)的分析與控制必將變得更加精細(xì)和重要。