《CMOS集成電路后端設(shè)計(jì)與實(shí)戰(zhàn)》是學(xué)習(xí)集成電路物理設(shè)計(jì)的經(jīng)典教材,其配套的Lab實(shí)驗(yàn)是掌握后端流程(從Netlist到GDSII)的關(guān)鍵實(shí)踐環(huán)節(jié)。獨(dú)立完成這些實(shí)驗(yàn)不僅能鞏固理論知識,更能培養(yǎng)實(shí)際工程能力。以下是一份詳盡的、手把手的自學(xué)指南,旨在幫助你脫離依賴,獨(dú)立攻克這些實(shí)驗(yàn)。

第一步:實(shí)驗(yàn)環(huán)境搭建與工具準(zhǔn)備

- 獲取實(shí)驗(yàn)資料:確保你擁有完整的實(shí)驗(yàn)數(shù)據(jù)包,通常包含標(biāo)準(zhǔn)單元庫(時序、功耗、物理庫)、設(shè)計(jì)網(wǎng)表(Netlist)、約束文件(SDC)、技術(shù)文件(Tech File)及腳本模板。

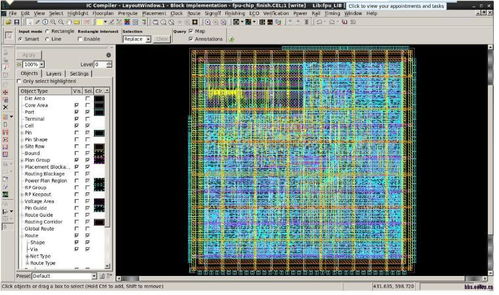

- 安裝EDA工具:實(shí)驗(yàn)通常基于Synopsys或Cadence等商業(yè)工具鏈(如Design Compiler, IC Compiler II/Innovus, StarRC, PrimeTime)。作為學(xué)習(xí)者,可以申請教育版License或使用功能受限的免費(fèi)版本。務(wù)必仔細(xì)閱讀工具的安裝與配置文檔,正確設(shè)置許可證和環(huán)境變量(如

LM<em>LICENSE</em>FILE,PATH)。 - 驗(yàn)證環(huán)境:運(yùn)行一個簡單的工具命令(如

icc2_shell -version或innovus -version)來確認(rèn)工具可正常啟動。嘗試用附帶的庫文件做一個簡單的讀入操作,確保數(shù)據(jù)格式無誤。

第二步:理論回顧與實(shí)驗(yàn)?zāi)繕?biāo)精讀

不要急于操作! 在打開工具之前:

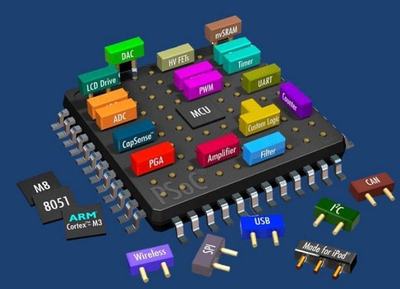

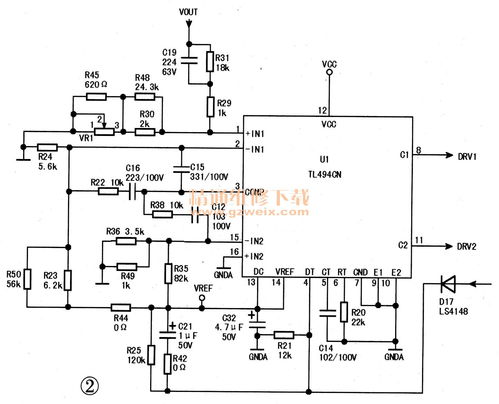

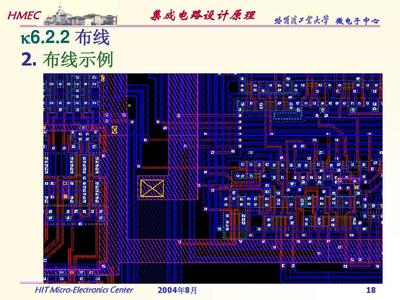

- 精讀教材相關(guān)章節(jié):明確當(dāng)前實(shí)驗(yàn)在完整后端流程(綜合、布局、時鐘樹綜合、布線、簽核)中的位置。理解每個步驟的目的、輸入和輸出。

- 逐字研讀實(shí)驗(yàn)指導(dǎo)書:

- 明確最終目標(biāo):例如,“在滿足時序約束的前提下,實(shí)現(xiàn)面積小于XX,功耗低于YY的物理版圖”。

- 理解每一步指令:弄清每個命令或腳本參數(shù)的意義。如果不明白,立刻回顧教材或工具手冊。

- 分析提供的腳本:實(shí)驗(yàn)通常會提供部分腳本。將其打開,加上自己的注釋,理解每一行的作用。這是學(xué)習(xí)自動化流程的最佳方式。

第三步:分步執(zhí)行與深度探索

遵循“運(yùn)行-觀察-分析-調(diào)整”的循環(huán):

- 從第一步開始:例如,數(shù)據(jù)準(zhǔn)備(讀入庫、網(wǎng)表、約束)。在工具命令行中手動鍵入關(guān)鍵命令,而非直接運(yùn)行完整腳本。觀察日志信息,確認(rèn)數(shù)據(jù)成功載入。

- 記錄與檢查:每完成一個步驟(如初始布局),立即使用工具提供的檢查命令(如

check_placement)并查看報告(面積、時序、擁塞報告)。將這些結(jié)果記錄下來,與預(yù)期對比。 - 遇到報錯怎么辦?:

- 精準(zhǔn)定位:仔細(xì)閱讀錯誤(Error)和警告(Warning)信息,工具通常會給出出錯的代碼行或?qū)ο竺?/li>

- 獨(dú)立排查:檢查文件路徑是否正確、文件格式是否匹配、變量是否定義、約束是否合理。這是培養(yǎng)debug能力的核心。

- 善用資源:將錯誤信息的關(guān)鍵詞在工具官方文檔、教材或Google(如“ICC2 ERROR ORD-...”)中搜索,絕大部分基礎(chǔ)問題都有解答。

- 超越實(shí)驗(yàn)指導(dǎo):在完成基本流程后,主動嘗試:

- 調(diào)整參數(shù):修改布局的密度目標(biāo)、時鐘樹綜合的緩沖區(qū)類型、布線的層數(shù)分配,觀察其對時序、面積、功耗的影響。

- 分析折衷:嘗試優(yōu)化時序(可能增大面積和功耗),或優(yōu)化面積(可能降低時序余量),理解后端設(shè)計(jì)中的權(quán)衡藝術(shù)。

- 可視化檢查:熟練使用工具的圖形界面(GUI)查看布局布線結(jié)果、時序關(guān)鍵路徑、電源網(wǎng)絡(luò)。直觀理解比看報告更深刻。

第四步:結(jié)果分析與復(fù)盤

- 收集最終報告:時序報告(建立/保持時間違例)、面積報告、功耗報告、DRC/LVS驗(yàn)證結(jié)果(如果實(shí)驗(yàn)包含)。

- 進(jìn)行結(jié)果分析:

- 你的設(shè)計(jì)是否滿足了所有約束?如果沒有,違例的主要原因是什麼?(是邏輯路徑太長?擁塞導(dǎo)致布線延遲過大?)

- 對比不同優(yōu)化策略下的結(jié)果,得出結(jié)論。

- 撰寫實(shí)驗(yàn)筆記:用你自己的話,記錄完整的操作流程、關(guān)鍵命令、遇到的錯誤及解決方法、最終結(jié)果和分析。這份筆記是你最寶貴的財(cái)富。

保持獨(dú)立性的關(guān)鍵心態(tài)

- 把工具當(dāng)作“黑盒”到“灰盒”:初期只需知道輸入輸出;后期應(yīng)通過文檔和實(shí)驗(yàn),逐步了解其內(nèi)部算法的基本原理。

- 問題分解:將一個大問題(如“有時序違例”)分解為小問題(是哪個寄存器?是哪條路徑?是布局問題還是布線問題?)。

- 耐心與堅(jiān)持:后端設(shè)計(jì)迭代周期長,一個實(shí)驗(yàn)可能需要數(shù)天甚至更久。每一次失敗和排查都在增強(qiáng)你的實(shí)戰(zhàn)能力。

通過以上系統(tǒng)性的方法,你將不再是被動地跟隨步驟,而是能夠主動掌控整個設(shè)計(jì)流程。你不僅能獨(dú)立完成這本教材的Lab,更將獲得應(yīng)對真實(shí)集成電路后端設(shè)計(jì)挑戰(zhàn)的堅(jiān)實(shí)基礎(chǔ)和自信。